Zdroj: datasheet W83627DHG, str. 176 PDF souboru (164 v tisku)

Jak je vlastně na motherboardu zařízeno, že po stisknutí slaboproudého tlačítka

začne počítač startovat?

Zvenčí je vidět, že "power button" je vstup s pull-upem na +3.3V,

který se tlačítkem krátce zkratuje k zemi, a zase pustí (uplave vzhůru).

Motherboard zareaguje tak, že "přitáhne k zemi" PS_ON#

vstup napájecího ATX zdroje (zelený drát), a drží ho dole.

Zdroj reaguje tak, že rozjede hlavní měnič, který živí silové napájecí větve.

Tím obživne procesor a začne vcelku známá bootovací sekvence: skok na well-known

adresu v ROM (startovní vektor), kterým začíná BIOS POST.

Aby logika kolem tlačítka fungovala, potřebuje motherboard od zdroje trvalé stand-by napájení:

+5VSB (fialový drát), původně stačilo cca 0.5A, dle ATX 2.0 už asi 2A, serverové

zdroje umí i víc (kolem 4A). Motherboard si z něj sám vyrábí +3.3VSB pro čipy,

které tuto hladinu vyžadují.

A to je všechno? No... pokud Vás zajímají detaily, zjistíte, že zdaleka není :-)

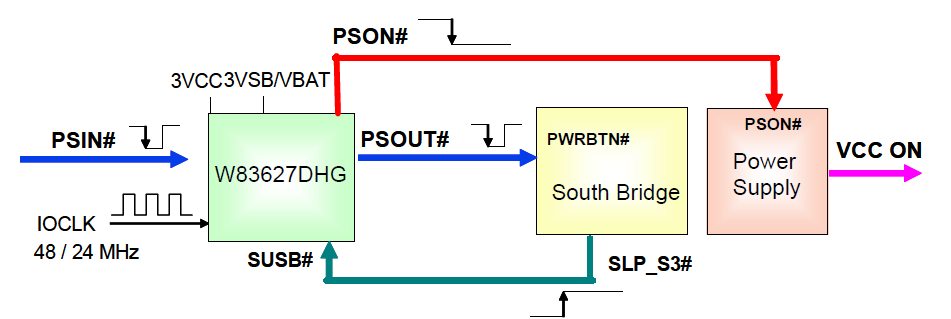

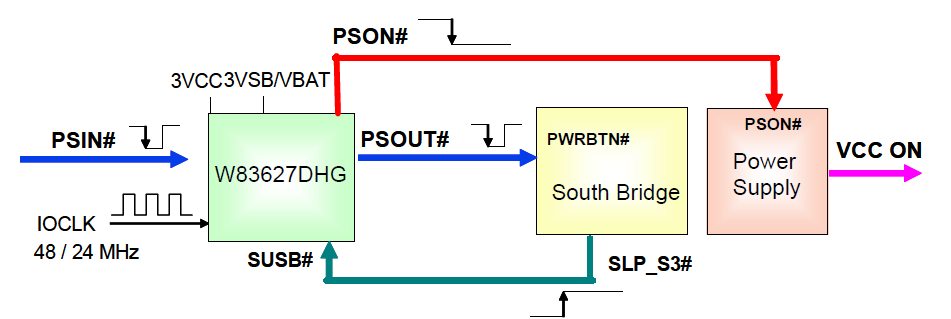

Zapnutí/vypnutí napájení v ATX motherboardu dělá z větší části SuperIO šváb. Přinejmenším v tom smyslu, že přijme vstup od tlačítka "power button" a otevřeným kolektorem na svém konkrétním pinu přitáhne k zemi PS_ON vstup zdroje.

Zdroj: datasheet W83627DHG, str. 176 PDF souboru (164 v tisku)

Z obrázku a doprovodného textu plyne, že je to celé trochu složitější:

rozhodnutí, zda zapnout, činí nakonec south bridge. Takže se v sekvenci

zapnutí počítače "dominově" uplatní postupně všechny čtyři signály:

SuperIO čip tedy spolupracuje se south bridgem, ve kterém je např. RTC a NVRAM.

SuperIO čip taky umí zařídit automatické naběhnutí po přivedení napájení.

Zálohovací baterka CMOS NVRAM (CR2032 apod.) ve skutečnosti nezálohuje

jenom konfiguraci v NVRAM, ale taky vybrané další obvody uvnitř south

bridge a SuperIO. V datasheetech SuperIO a south bridge bývá přehled,

které vnitřní bloky jsou zálohované baterkou.

V datasheetu SuperIO lze dohledat konkrétní konfigurační registr

(týká se "ACPI device") a v něm asi dva bity, které říkají,

zda má počítač po naběhnutí napájení rovnou startovat, nebo zůstat ležet,

nebo "podle předchozího stavu" = SuperIO šváb si díky baterce pamatuje,

jestli posledně proběhl košer ATX power-down v jeho režii, nebo jestli

napájení padlo samo od sebe. (A někdy ta logika nefunguje správně,

nebo je bug v BIOSu který to špatně nakonfiguruje apod.)

Tyto signály dokážou zařídit, aby se počítač sám probudil.

PME# je vstup south bridge nebo PCI bridge.

V PCI sběrnici je to jediný drát s jednoduchou funkcí:

pokud za něj někdo zatahá v některém stand-by stavu

(ACPI S3/S4/S5,

tzn. spánek, hibernace nebo power off), motherboard by měl nahodit zdroj

a začít startovat - jako při stisku tlačítka "power button".

South bridge čip je BIOSem (nebo OS?) nakonfigurovaný, zda má reagovat

na PME# nebo ho ignorovat - toto nastavení je zálohováno napájecí

větví +5VSB. (Přesněji řečeno: dle dokumentace Intel ICH4

je dotyčný konfigurační bit PME_EN podepřený dokonce baterkou,

protože sdílí napájení s RTC obvodem - ale výpadkem stand-by

napájení je bit PME_EN resetován, přinejmenším v tomto čipsetu.

Takže po výpadku napájecí sítě přestane probouzení fungovat.)

V některých BIOSech v SETUPu existovala volba "PME# enable",

v jiných BIOSech bývaly "lidsky" pojmenované volby

"povolit probuzení zařízením A/B/C/D/E".

Mohlo to být pohromadě v menu zvaném "power management" apod.

Také SuperIO čip má pin PME#, což je v jeho případě výstup. Tento sdružuje interní signály SuperIO čipu, dílčí interní PME# větévky, schopné probudit počítač - tradičně třeba od sériových UARTů (on-chip bloky uvnitř SuperIO) ale ono to reálně vypadá, že pomalu kterékoli zařízení uvnitř SuperIO má schopnost počítač probudit. Podle popisů konfigurací jednotlivých on-čip periferií uvnitř SuperIO se zdá, že PME# je navázán na IRQ výstup dané periferie, a tedy jeho přesná funkce závisí dále na konkrétní konfiguraci zdrojů přerušení uvnitř dané jednotlivé periferie. Třeba sériový port umí generovat interrupt na základě několika zdrojů/událostí. Buzení počítače se tradičně dělo na základě diskrétního modemového vstupu "ring" (vyzvánění = někdo nám volá).

Vedle "legacy PC" periferií uvnitř SuperIO, a klasicky třeba PCI síťovek (WoL), se umí počítač probudit také podle některých časovačů (modernější RTC, HPET).

Velmi na okraj připomeňme, že v dnešní době je SuperIO šváb

(v notebooku jeho příbuzný Embedded Controller) propojen se

south bridgem datovou sběrnicí LPC, což vlastně zúžená ISA.

(Hodně dávno skrz PCI, VL BUS nebo ISA.)

Tato sběrnice funguje jenom ve chvíli, kdy má čipset kompletní

napájení = počítač je v bdělém stavu. Proto se věci okolo napájení

signalizují "out of band", k tomu určenými diskrétními dráty.

Přesněji řečeno, takhle to

bylo

ještě v dobách

PCI,

a dodnes takto části motherboardu fungují.

Jak to ale funguje nativně na sběrnici

PCI Express?

To je sběrnice, která se vyznačuje silně redukovanou sadou vodičů,

je sériová, třeba interrupty se signalizují jedině zprávami.

Pokud se podíváte na pinout slotu PCI-e, najdete signál WAKE#, což zní slibně. Ano přihořívá, ale ten obrázek není zdaleka kompletní.

Volně parafrázováno ze

specifikace PCI-e

(str.429, začátek kapitoly 5.3.3):

Mějme periferní zařízení, které má v úmyslu probudit svůj hostitelský počítač.

Kýžená událost nastala, jdeme na to.

Jeho PCI-e uplink ale spí, PCI-e lane na upstream portu (linkový budič)

nemá napájení, netikají hodiny, vládne ticho a tma. V první fázi proto

musí periferie nějak vzbudit upstream PCI-e switch, resp. spíš rovnou

celý motherboard. Toto může provést jedním ze dvou způsobů (nebo oběma):

Různě po webu se lze dočíst, že věci nejsou až tak jednoduché. Zejména, pokud je třeba řešit návaznosti v ovladačích, pokud zároveň s probuzením periferie pošle interrupt apod. Možná je ale důležité především to, že se počítač vůbec probudil. Která periferie budíček poslala, to pro spoustu použití možná není moc podstatné - OS se vzbudí, příslušná serviska prohrábne načasované úlohy, rozmyslí se co dál, pokud byl počítač jenom uspaný tak user-space software visící na zařízeních začne zkoumat, jestli není něco nového apod. Tohle přeci nemusí/nemá řešit ovladač zařízení.

V hardwaru je několik míst, kde je třeba cosi odšpuntovat, aby probouzení fungovalo.

Jsou toho řekněme 3 úrovně:

Dokumentace PCI a čipsetů k tomu obvykle říká, že tyto konfigurační volby

mají ignorovat signál RESET (nemají zapomenout konfiguraci), což se

týká i situace, kdy deska projde stavem stand-by.

To prakticky znamená, že příslušné registry mají být napájené větví +5VSB.

A taky z toho plyne, že při odpojení napájecí šňůry se konfigurace

ztratí - až na případné výjimky, které jsou podepřené baterkou

(ale takové snad ani nejsou) nebo mají svoji konfigurační EEPROMku,

kterou čip načte okamžitě po přivedení napájení (typicky síťové čipy).

Povolit či zakázat jednotlivé konfigurovatelné bity/flagy může buď BIOS

nebo operační systém. Otázkou je jejich vzájemná koordinace a úcta.

Obecně má BIOS přístup ke všem konfigurovatelným věcem v čipsetu,

a některé na konci POSTu zamkne aby další software (OS, včetně ovladačů)

už s nimi nepohnul.

Nicméně se zdá, na základě praktických poznatků uživatelů napříč internety,

že BIOS obecně nekazí operačnímu systému konfiguraci probouzecích "tlačítek"

v čipsetu - ačkoli by mohl, pokud operační systém při vypnutí/usnutí

košer zavolá službu BIOSu nebo nějakou ACPI metodu.

Staré BIOSy mívaly globální PME# enable, případně povolení probouzení

od jednotlivých "legacy" periferií v SuperIO, které nejsou PCI zařízeními,

nemají PCI config space a proto nejsou příliš konfigurovatelné z vyššího OS.

Poslední dobou jsou BIOSy naopak vysloveně skoupé na konfiguraci per-slot

vlastností PCI(-e) - a že třeba konfigurace ASPM by se často dost hodila.

Takže nepřekvapí, že v BIOSu nelze nastavit zmíněné generické per-device

flagy druhé úrovně v PCI config space (přestože i na ně by BIOS klidně

dosáhl, kdyby chtěl). Tato konfigurace zůstává odemčená pro generický

přístup z OS. A snad až na výjimky (snad sériový port, nebo síťovky

doprovázené option ROMkou) BIOS nesahá na specifickou konfiguraci

"zdrojů PME#" uvnitř periferních zařízení. (Čest výjimkám mezi

BIOSy, které jsou podrobněji konfigurovatelné. Občas člověk potká

zajímavý kousek na značkovém HW nebo i na slušném "neznačkovém"

motherboardu.)

I pokud se povede nastavit nějaké probouzecí volby v BIOSu,

třeba ohledně SuperIO (sériové porty), je třeba mít na paměti,

že tato konfigurace se nejspíš ztratí při odpojení napájení,

a obnoví se až po dalším průchodu POSTem. Tzn. pokud počítač

po přivedení napájení zůstane ve stavu "ATX power off" (S5),

což si SuperIO pamatuje protože tato funkce je podepřená baterkou,

patrně nepůjde probudit sériovým portem, pokud to není

factory default daného čipu (protože příslušný registr

závisí na +5VSB). Této věci se obvykle netýkají

"straps" ať už fyzické (alternativní funkce pinů) nebo

"soft straps" (v nějaké EEPROMce - konkrétně SuperIO ale

žádnou nemá).

Pod Windows je v device manageru na PCI zařízeních zhusta k vidění

konfigurovatelná fajfka "povolit zařízení probouzet počítač".

Detailní konfigurace "zdrojů událostí pro probuzení" je věcí

ovladačů nebo doprovodných utilit, které jsou HW-specifické

pro danou periferii. Například na základě jakých druhů paketů

má síťovka se zapnutou funkcí WoL počítač probudit. Pokud mohu

soudit, na sériovém portu toho člověk pod Windows moc nenakonfiguruje,

protože odmaskování konkrétních zdrojů interruptu v UARTu

si generický ovladač dělá po svém a nelze to uživatelsky

či programově konfigurovat.

Konkrétně síťové karty majú své špecifiká.

Klasická stand-alone síťová karta má malou konfigurační EEPROMku,

(93c46, 24c01 apod) ve které je MAC adresa, nastavení rychlosti/duplexu,

WoL a dalších věcí. Lepší síťovky mívaly také flashku (cca do 32 kB),

ve které byl uložen BIOSový modul zvaný "option ROM", který si hostitelský

BIOS natáhne při POSTu. K síťovkám se tradičně dodává stand-alone

uživatelská utilita, která umí upravit konfigurovatelné atributy

(a obvykle taky integrátorská utilita, která umí změnit i MAC adresu.)

Ovšem pozor: síťovky integrované na motherboardu nemívají option ROM

ve vlastní malé flashce, ale integrovanou v hostitelském BIOSu.

Dokonce nemusí mít ani konfigurační EEPROMku, pokud do nich MAC adresu

nasype při POSTu hostitelský BIOS - ale taková síťovka je problematicky

použitelná pro WoL (po studeném startu nebude mít síťovka MAC adresu.)

Nastavení WoL lze jistě zařídit i v operačním systému, pokud má ovladač

příslušné volby - ale toto si síťovka bude pamatovat pouze do výpadku

napájení. Co má uloženo v konfigurační EEPROMce, to platí i po studeném

startu.

Závěrem dvě příhody z natáčení:

PCI sběrnice se v průběhu let vyvíjela, od pradávné verze 1.0

přes 2.0, 2.1, 2.2, 2.3 až po nepříliš známou 3.0. Proto si někteří

výrobci motherboardů a karet vykládají význam některých pinů různě,

případně "reserved" piny nekorektně uzemní apod.

(Stanou se i horší přehmaty, ale o tom kdyžtak u piva.)

Například bylo nebylo, existovala periferní karta, jejíž výrobce

si patrně špatně vysvětlil logiku PME#, a proto příslušný pin

na kartě spojil s +3.3V, asi jako že "já přece rozhodně

počítač budit nebudu". No a když se taková karta zasunula

do motherboardu, který PME# ctil, tak milý počítač nešel

vypnout! Po vypnutí tlačítkem nebo softwarově z OS počítač

jenom krátce mrknul LEDkami a začal znovu startovat.

Proč? Protože silová větev 3.3V se po vypnutí stroje

rychle vybila a stáhla PME# ssebou pod log.0.

Čímž se počítač znovu nastartoval.

Workaround: zakázat v BIOSu PME#,

nebo přelepit PME kontakt na kartě izolepou.

Jiná humorná příhoda: bylo nebylo, v jedné skládačkové

PICMG sestavě (pasivní backplane s 14 sloty, do něj zasunutá

CPU karta) osadil zákazník asi tři dvouportové optické síťové karty

s čipy AMD. Tyto čipy měly trvale zapnutou funkci WoL - snad i

šla softwarově vypnout, ale jenom do tvrdého odpojení napájení.

Po vytržení "ze zdi" a novém přivedení napájení počítač

nechtěl nastartovat. LEDka indikující přítomnost +5VSB mžourala.

Tuším se dal nastartovat "drátem" (tvrdým zkratem PS_ON na zem.)

Důvod? Každá ze tří optických síťovek žrala ve stand-by díky WoL asi 1A.

Plus něco si bral motherboard. Použitý zdroj odpovídal ATX 2.0,

jeho větev +5VSB uměla 2A.

Workaround: přelepit napájení 5VSB na kartách izolepou.

Zdroj ve formátu PS/2 s podporou víc jak 2A +5VSB nebyl k dispozici.

Serverové zdroje umí víc, ale jsou rozměrnější.

K čipům AMD buď neexistovala konfigurační utilita pro jejich

doprovodné EEPROM, nebo tuto volbu neposkytovala... prostě tudy

cesta taky nevedla.

A to by asi pro dnešek stačilo...

Sepsal: František Ryšánek (rysanek [AT] fccps [dot] cz)